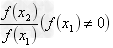

L6561 功因校正相关原理 (1) 功率因子的定义 将一弦波电压 Vs(t)= 2 Vrmscosωt 加于一负载, 则所得到之电流为 i s(t)= 2 Irmscos(ωt-ψ1),其中ψ1 为电流与电压之相角差。其中功率因子为: PF= p s = cosψ1 若电流为非弦波时(如输入电压经全波整流后之电流)则含有谐波成份,此电 流之谐波成份亦为影响功率因子之因子。 i s(t)= 2 I1cos(ωt-ψ1)+ΣIncos(nωt-ψn) I1 : Fundamental 电流 In : n 次谐波之电流 Irms : (I20+ I21 +I22+. . .I2n)1/2 I0 : 电流之 DC 成分,若在纯 AC 电源中则 I0=0 重新定义 PF: PF= [I1/ Irms]×cosψ1= [I1/(I20+ I21 +I22+. . .I2n)1/2] × cosψ1 其中 cosψ1 : Displacement Power factor (DPF) 电流失真成份 Idis= [I2rms-I21]1/2 又可将电流谐波失真的程度表示为 (%THD)= (Idis /I1) × 100% (2) 升压型高功因直流转换器 传统的转换器,为获得较小的涟波的电压,通常于全桥整流完后加入一个 大电容;但大电容意味着在大部分的时间里,线电压都是低于电容电压,也就是 整流二极管的导通时间减小,导通时电流增大,进而造成线电压的失真。 现今则于整流器与输出间插入一级功因校正器电路, 以使输入电流近似 SIN 波形,同时保持与电压同相(In Phase) 。理论上任何的拓朴结构都可以达到高功 因的要求,实际上则使用升压型结构来实现,其理由如下: 1. 使用较少的零件,可以降低成本。 1/24 di 较小,噪声的产生较小,EMI 滤波器可以较小。 dt 3. 开关晶体因为共源级,所以较易驱动。 2. Boost 电感的 其缺点为: 1. 输出直流电压一定要高于输入峰值电压。 2. 由于输出入没有隔离,所以输入突波易在输出端出现。 目前采用二种方法来作 PFC 控制: 1. 固定频率平均电流法:需复杂的控制。Uc3854 2. 固定导通时间、但频率可变的瞬时模式法(L6561 采用此法) 。 操作原理: 图 1 是本文所采用的电路架构,其转换器部份乃由功率二极管 D1 、D2 、 D3、D4 所组成的桥式整流电路, 串接一升压电感 L, 经由适当的控制功率开关 Q, 以调整输出直流电压 Vdc 的大小,并使输入电流自动追随输入电压成为同相位, 进 而达到高功因的要求。 由功率开关 Q 之切换控制,可使得升压电感上的电流操作于边界导通模式; 其工作原理可以下列Ⅰ、Ⅱ两个操作模式来说明: L D + Q D4 D3 D1 D2 vS CO Load Vdc _ 變頻控制 图1 模式Ⅰ: 升压型转换器电路架构图 功率开关 Q 导通时, 构成的等效电路如图 2 所示, 转换器将形成两个独立的回路。 回路 1 是输入电源 v s 对升压电感 L 储能;回路 2 则是由输出电容 Co 与负载所组成, 2/24 此时输出电容将原先所储存之能量提供给负载以维持输出电压 Vdc 。 L D + Q D4 D3 D1 D2 vS CO Load Vdc _ 图2 模式Ⅱ: 功率开关 Q 导通之等效电路 当功率开关 Q 截止,且升压电感 L 之电流大于零时,其等效电路如图 3 所示, 此 时输入电源 vs 及储存于升压电感 L 之能量,一起对输出电容 Co 充电并提供能量给负 载。 L D + Q D4 D3 D1 D2 vS CO Load Vdc _ 图3 功率开关 Q 截止之等效电路 若输入交流电源电压为 v s ( t ) 为: = V m sin ω t ,则由图 2 可得到电感电流的峰值 v ( t ) ? Ton V m ? D ? T s i pk ( t ) = s = sin ω t L L 其中 Ts 为功率开关 Q 之切换周期(Switching period), D 为责任周期(Duty cycle)。 由上式可以得知,在一输入电压周期内,若功率开关之导通时间保持一定,则电感峰 3/24 值电流的联机将会成为一个 I p ? sin ωt 的波包,如下页图 4 所示,使得输入电流与 输入电压为同相位,达到高功因的要求。由上式可得电感峰值电流之最大值 I p 为: V ?T π V ?T I p = m on sin( ) = m on L 2 L (1-2) 图4 电感电流波形 基于上述之原理,为了使功率开关的导通时间保持一定,以避免输入电流产生 失真,故整个系统回路的交越频率必须远小于输入电压之频率。 (3) L6561 特点、方块图介绍 L6561 是 L6560 的改良版,具有优越的乘法器,在 universal 输入电压时能获 得较佳的 THD 值;同时启动电流亦减低至几十个 uA,而 ZCD(零电流侦测)也具有除 能(Disable)的功能。此外还具备精准的内部参考电压(1%误差) 、输入电流感测端 的内部 RC 滤波器、输出 400mA 能力等等。 此 IC 操作在瞬时模式(即边界导通模式),可用在电子式安定器、AC-DC 转换 器及切换式电源供应器。 L6561 主要特点: 1. 具磁滞的欠电压锁住功能。 4/24 2. 3. 4. 5. 6. 7. 8. 9. 低启动电流(典型值:50uA;保证 90uA 以下) ,可减低功率损失。 内部参考电压于 25℃时只有 1﹪以内的误差率。 除能(Disable)功能,可将系统关闭,降低损耗。 两级的过电压保护。 内部启动及零电流侦测功能。 具乘法器,对于宽范围的输入电压,有较佳的 THD 值。 在电流侦测输入端,具备内部 RC 滤波器。 高容量的图腾级输出,可以直接驱动 MOSFET。 其脚位图如下页图 5 所示。 图5 L6561 接脚功能如下: PIN 脚 1 2 3 4 5 6 7 名 称 INV COMP MULT CS ZCD GND GD L6561 脚位图 功 误差放大器反相端输入 误差放大器输出 乘法器输入 能 利用电流侦测电阻 Rs,将电流转成电压输入 零电流侦测 接地 为 MOSFET 闸极驱动输入 5/24 8 VCC L6561 的输入工作电压 6/24 方块图描述: 1. 电源供应方块图: 图 6 电源供应方块图 如图 6 由 Vcc 供应电源给’线性电压调整器’,产生 7V 的内部电压,以供给 IC 使用,但输出级则直接由 Vcc 供应。另外 BandGap 电路产生一个精准的内部 2.5V 参 考电压,可用于控制,以达到良好的输出调整率。 如图 7 所示,具备磁滞功能的欠电压锁住(UVLO)比较器,用以确认只有 Vcc 电压足够高时,IC 才会致能,已获得较佳的信赖性。 7/24 图 7 欠电压锁住方块图 2. 误差比较器及过电压保护方块图: 如图 8 所示,误差放大器的反向输入端,经由外部串联分压电阻与输出端 连接,以取得一部分的输出电压,并与内部参考电压做比较,以获得固定的直流 调整电压。 误差放大器通常在输出端与反向输入端之间,使用一个回授电容以作为频 率补偿,因为在半周期内,误差放大器输出必须维持定值已获的高的 PF 值,所以 需要很低的频宽。 为了误差放大器在过电压造成的低饱和,或过电流造成的高饱和之后能快 速回复,误差放大器的动态输出电压被内部箝位电路限制在 2V 到 5.8V 间。 此 IC 提供二级的过电压保护; 于过电压时, 误差放大器的输出趋向低饱和, 但误差放大器响应很慢,所以它会维持一段时间才进入饱和区。但另一方面,一 个过电压必须被立即修正,因此一个基于不同观念的快速过电压保护是必要的。 因为电容并不允许直流电流流过,于稳态时流过 R1 与 R2 电阻的电流是一 样的。 当输出电压因一个负载步阶改变而上升,R1 电流亦跟着上升,但 R2 电流 则因电压固定于 2.5V(因误差放大器反应较慢)而不改变,增加部分的电流则流 经补偿电容,进入误差放大器的输出端,当感测到此情况时,两阶段处理程序将 发生(如图 9 所示) : ’Soft Braking’:当电流超过达 37uA 时,乘法器的输出电压将强迫下降,如 8/24 此从电源端汲取的能量将会降低,也降低输出电压的上升额度。如此能避免输出 电压超出默认值太多,而达到保护功能。 图8 误差比较器及过电压保护方块图 图 9 过电压动作保护图 假使输出电压忽略了’Soft Braking’的作用而持续增加,导致进入 E/A 的电流 9/24 达 40uA,系统将进行’Sharp Braking’:乘法器的输出端将被拉到低准位,MOSFET 输出级关闭,同时内部启动器也将关闭。当 E/A 的输入电流降低至 10uA,因内部 电流比较器提供磁滞的功能,因此输出级将从低准位被释放,而再一次致能。以 上’Soft Braking’及’Sharp Braking’称为动态过电压保护,他们大部分(非全部)皆 能有效防止因负载突变而生的问题;事实上,他们对输出电压的变化较为敏感。 但对于像负载移除而产生的稳态过电压,则无法提供好的保护。 当过电压持续一段时间(E/A 的输出电压低于 2.25V) ,稳态过电压保护将被 执行:除了将输出级及外部 MOSFET 除能外,亦将内部一些方块功能除能,静态 电流降至 1.4mA;当 E/A 的输出电压回到线性区时,系统将再次致能。 3.零电流侦测及触发方块图: 如图 10 所示,当电感电流减小到零后,ZCD 方块功能将会使 MOSEFT 致能, 使跨于电感上的电压反转。当电路于运作状态时,ZCD 的讯号乃是藉由 Boost 电感 的辅助绕组而来;ZCD 没有讯号时,可由内部启动器(Inter Sarter)藉由强制驱动 器(Driver)送出一脉冲讯号给 MOSFET 闸级以将外部 MOSFET 启动。内部启动 器的重复率大于 70ms(大约 14KHz),所以在设计时,最大频率必须被考虑。 图 10 零电流侦测及触发方块图 4.除能方块图: 如图 10 所示,ZCD 脚亦可同时致能除能方块;当此脚的电压低于 150mV, 系统将被卸载,消耗将降低。欲重新致能系统,则需将此脚的低电位移除。 5.乘法器方块图: 如图 11 所示,乘法器具有两个输入端:第一个为与输入整流电压成一比例的 取样电压,另一个为 E/A 的输出电压;假若 E/A 的输出电压在半个周期内为定值, 则乘法器的输出亦将会是整流后的 SIN 波形, 并将此信号作为电流比较器的参考讯 10/24 号。而在各周期内,电流比较器限定了 MOSFET 的峰值电流。 图 11 乘法器方块图 6.电流比较器方块图: 如图 12 所示,电流比较器感测到跨于电流侦测电阻(Rs)上的电压,并拿此讯 号与乘法器输出的规划讯号做比较,以决定 MOSEFT 真正关闭的时间。另 PWM 栓 锁则可避免因噪声而造成 MOSEFT 误切换。乘法器的输出被内部箝位器限制于 1.7V;当 Rs 上的电压到达此值,则电流的极限值亦跟着出现。 图 12 7.驱动器方块图: 电流比较器方块图 11/24 如图 13 所示,具有 400mA 供应 / 沉入能力的图腾级输出,能够驱动外 部 MOSFET。当系统发生欠电压锁住(UVLO)情况,内部 Pull-Down 电路将输出固定 在低准位,以确保外部的 MOSFET 不会意外地被触发。 图 13 瞬时功因校正器(T.M. PFC)操作: 驱动器方块图: 交流主电源经过桥式整流后送入升压型转换器;使用切换技术的升压型转 换器,可将输入电压转换到我们需求的输出电压值。电路结构如下图所示: 图 14 电路结构图 L6561 使用所谓的瞬时模式技术(Transition Mode Technique)来达到使输入电 流为 Sin 波形、及电流与电压同相位的目的。 误差放大器将升压转换器输出的取样电压与内部参考电压做比较,并产生正比 于两者差的讯号;若误差放大器的频宽足够小的线Hz) ,则此误差讯号于半 周内可视为一直流值; 此误差讯号将被送入乘法器,并与整流后的输入取样电压做乘绩,乘积结果为 一整流过后的 Sin 波形,其峰值大小与主电压峰值及误差讯号量有关。 乘法器的输出送入电流比较器的’+’端,为 PWM 之 Sin 波形的参考讯号;事实 上,当 CS(即 pin4)的电压(为电感电流与电阻的乘积)与电流比较器 ’+’端的电压 12/24 相等时,MOSFET 的导通动作就被截止。若依此推论,则电感电流的封包将是整流过 后的 Sin 波形。在每一个半周的操作过程,证明系统有固定的导通时间是可能的。从 MOSFET 截止到电感电流为零时,电感对负载做放电释能动作;当电感电流为零, 电 感上无储能,而泄极(Drain)处于浮接状态,此时电感与泄极的总电容产生共振; 泄 极的电压快速掉落到实时线电压之下,而 ZCD 讯号又再次触发 MOSFET 导通,另一 转换周期也跟着开始。 跨越 MOSFET 上的这个小电压,在导通时可以减小切换损失及储存于泄极等 效电容的能量(损失于 MOSFET 内部)的损失。 如图 15 所示为电感电流与 MOSFET 于时间区间之结果;藉由几何学的关系可 证得,从主线路撷取的输入平均电流,恰好是电感峰值电流波形的一半。 系统操作介于连续与不连续的临界模式(虽非正确但已接近) ,这也就是为何 称系统为瞬时模式的功因校正器(TM PFC)的原因。 图 15 电感电流与输入平均电流图 除了简单、外部零件少、及电感体积小(因小电感值)外;因在电感上有高涟 波电流(意味着在整流完后的主回路上拥有高有效值及高噪声之电流) ,所以需要一 个 EMI 滤波器来抵制噪声; 这个缺点限制了瞬时模式功因校正器, 应用于低功率范围。 应用电路: 图 16 应用电路图 13/24 输出电压经 R7、R8 分压后,可于 pin1 得出正比于输出电压之回授电压,此电压 与 IC 内部 2.5V 之参考电位做比较后,再经 pin1 与 pin2 两端之补偿网络输出,以作 为内部的乘法器输入之一;同时 60Hz 电源电压经 R9、R10 分压,于 pin3 得到一弦波 电压 Vs(t),亦为乘法器的另一输入源,这两个电压经乘法器乘绩后,可得一比例之弦 波参考电压 Vr(t),此弦波参考电压 Vr(t)乃做为功率开关截止时机之依据。当 pin7 闸极 驱动信号使 MOSFET 导通时,电感电流依 di/dt 斜率上升,流经 sense resister R6,取 电阻 R6 之跨压 V4 经 pin4 与参考电压 Vr(t)做比较,当 V4>Vr(t)时,pin7 pull down, 使 MOSFET 截止。choke 中,另一组辅助线 稳定电源外,另提 供 switch 导通之控制。当 MOSFET 截止时,主线圈极性反转,辅助线圈此时 dot 为 正电位,提供 pin8(Vcc)电源与 pin5(ZCD : zero current detector)之参考电位。当主线圈 之能量释放完毕时(因工作于 continuous and discontinuous boundary,此时电流为 0), 辅助线圈之电位亦下降,所以 pin5 之参考电位随之下降,由于 ZCD 内部电路为负缘 触发, 在下降至 1.8V 以下时则触发内部之 RS flip-flop 使 pin7 pull high 而使 MOSFET 导通。 因此可看出经由主动式 PFC 所得之平均电流波形为一完整之弦波,且其相位 与 AC 电源同相。经由主动式功率因子校正所得之 PF 值可达 0.98 以上。 14/24 设计准则: 以下描述一些设计准则,基本的设计规范考虑以下数据: ? 主输入电压范围:Virms(min) ~ Virms(max) ? ? ? ? ? ? ? ? ? 输出直流电压值:Vo 额定输出功率:Po 最小切换频率:fsw 最小输出电压涟波:ΔVo 最大公认超越电压:ΔVovp 期望效率:η 输入功率:Pi(= Po/η) 最大主有效值电流:Irms(=Pi/Virms(min)) 额定输出电流:Io(=Po/Vo) 电源部分设计: 输入桥式二极管: 输入桥式整流:使用标准慢速、低价的二极管即可。必须考虑最大输入电流 (Irms) ,最大峰值电压及二极管相关的热资料。 输入电容: 输入高频率波电容(Cin)可减少来自高频电感电流涟波的切换噪声。最差 的情况将发生于最小额定输入电压的峰值时,最大高频涟波电压通常被抑制于最小 输入额定电压的1﹪到10﹪之间,可藉由一系数表示(r=0.01到0.1) 。但实际则需将 EMI滤波器也考虑进去。 输出电容: 输出电容与直流公认突波输出电压值、输出功率和期望的电压涟波有关。当 选择一个低ESR值的电容,其值为 其中f为主电源频率;ΔVo通常为输出电压的1﹪到5﹪。 假若考虑系统的保持时间,则采用下列公式 15/24 Vo_min是考虑负载调整及输出涟波电压值的最小输出电压; Vop_min则是系统侦测 出藉由PFC 所供应的电源失败(Power Fail)之前,最小输出操作电压。 升压电感: 设计电感包含许多的参数,也有不同的方法可以使用。首先电感值必须先定义, 使系统最小的切换频率大于内部启动器的最大频率,以确保系统于正确的TM操作。 假设为单位功因,则 其中 :为电感电流的最大值;Ton、Toff:为开关的ON、OFF时间。而 线频峰值电流(与输入功率及线电压有关)的两倍,即 为 将上述的关系式,用Ton、Toff表示,经过代数运算,可以算出在一周期内的实 时切换频率为 fsw最小值发生于线?) ,最大值发生于线?) ; 最小系统切换频率可能发生于最大或最小线电压。者电感值定义如下 式中的Virms可以为Virms(min)或Virms(max),不论何者都给电感较小的值。最小 的切换频率建议为15KHz,以不干扰内部启动器。电感值已定义完成,则实际的设计 可以开始: 考虑磁性材料、几何形状(因高电压造成需要隔离)、操作频率范围,选择高频 亚铁盐(Ferrite)材料、具空气心、绕线架的铁心组。由于供应厂商制作的型式有很 多变化,最终选择以技术及经济上的考虑为主。 铁心尺寸的大小,采用以下的经验公式: 其中体积单位为 ;电感单位为mH。 接着绕组必须被定义,线圈数与绕线面积须被量化;储存于电感的最大实时能量 为 可储存于磁场内(可由最大能量密度与铁心有效体积【Ve 】的乘积表 16/24 示之) ,即 式中的Ae为铁心有效截面积,Ie为有效磁通路径的长度(两者皆可由铁心的数 据中找到) ,ΔH为磁场强度的变化量,ΔB为磁通密度的变化量。 未避免因高导磁率而造成铁心饱和,及允许足够的磁场强度变化量,使用一个 气隙是必要的。尽管气隙长度Igap为Ie的很小百分比值,亚铁盐(Ferrite)铁心的导磁 率是很高(典型值为 ),假定所有的磁场皆集中于气隙是可能的,且有良好 的近似值( );例如1﹪的Igap/Ie(为最小的建议值)约与假设值有 4﹪的 误差;假若Igap/Ie值越大,则误差将会减少。 忽略气隙区域边缘的漏磁,能量平衡重新写成 通过铁心及气隙的ΔB为磁通密度是一样的,且与气隙中的磁场强度有以下的关 系: 于气隙区域使用安培定律,可得 从能量平衡关系式可以得出 式中的N是绕组的圈数。 N若决定了,建议确认铁心是否饱和;若是结果太接近临界值,则需增加气隙 的距离,并从新计算一遍。绕线之选择则需考虑铜损大小能在可接受的范围: Rcu由于受到高频涟波影响,使集肤及邻近效应变明显,造成损失增加;所以建 议使用Litz线或多股线。最后绕线的面积需要被考虑;若是使绕线架的绕线面积不符, 则考虑使用一个更大的铁心组,并重新计算绕组。 为了使ZCD脚能辨别电感电流流到零,增加一辅助绕组是必须的;采用低售价 及细薄的绕线组。绕线的圈数是唯一需要被定义的参数。 功率MOSFET: 17/24 MOSFET的选择主要考虑与输出功率相关的 ;由于输出电压将晶体的反向 偏压电压给固定住了,故考虑耐压时就需加上最大突波电压及安全余裕度等因素。 导通损失(Conduction Loss)如下式所示: 其中 切换损失(Switching Loss)是因于TM操作下,在晶体关闭(Turn-off)时电流电压面 积交叉所造成 式中的tfall是晶体关闭时的交越时间(Crossover time) 。 而晶体导通时(Turn-on)的损失则导因于MOSFET内部的泄极总电容放电,其 值如下式: 式中的 是MOSFET的泄极内部电容; 和 是外部寄生总电容; 是MOSFET 于导通时泄极的电压。 因为 是沿着每半周期输入电压在改变的, 特别是 ,不仅受到输入SIN电压波形变化而改变,还受到升压电感与泄极总电容造成 谐振而产生的电压降影响(如图17) 。在经验上对总切换损失做一粗略的估算是可行 的。因此于在低电压输入时, 在每半周期的特定部分,将会为零。 图17 升压二极管: 泄极电压图 18/24 此飞轮二极管需采用快速型的;直流( DC)电流值和有效值( RMS)电流值对 于损失的计算是非常有用的,表示如下 导通损失可以用下是估计: 式中Vto(临界电压Threshold Voltage)和Rd(差动电阻Differential Resistance) 皆 是二极管的参数。至于反向偏压和MOSFT一样。 偏压电路 第一脚(INV) : 与E/A的反向输入端及OVP电路相连接,一个分压电阻串于输出电压端与此脚之 间。内部E/A之非反向输入端有2.5V的参考电压。内部OVP警告电流为40uA;R7、R8 的选择方法如下: 第二脚(COMP) : 为E/A输出端,同时亦为乘法器的两个输入之一;一个回授网络置于此脚与第一 脚之间,此补偿网络借着减小频宽以避免系统的干扰,以便控制输出电压的涟波 (100~120Hz) 。 最简单的情况为一颗电容当成补偿网络,它提供了低频率极点和高的直流增益; 一个简单的标准可以定义此电容值:即设定频宽为20~30Hz之间。 第三脚(MULT) : 为乘法器的第二输入脚;经由分压电阻,取得SIN输入波形的一部份电压,来当 成参考信号。乘法器可由以下关系描述: 19/24 Vcs(乘法器输出)为电流感测的参考讯号;K为乘法器的增益。一个完整的描 述如图18所示;它显示了乘法器的特性曲线V可以 保证乘法器操作于线性区域;而在特性曲线族中, 的最大斜率值至 少有1.65。基于这个考虑,可以依以下的方法,来设定乘法器的适当工作点: 首先选择VMULT的最大值VMULT PKX(发生在最大输入电压时) 。所以在宽范 围输入时,此值应该在3V或其附近在;而在单输入电压时,此值应该要少一点。最小 的峰值发生于最小输入电压时,表示如下 此值乘于 的最小保证值,将得到乘法器的最大峰值输出电压 如果 并从新计算。则 超过电流感测1.6V的线性区域,则必须取一个较小的VMULT PKX, R10的选择:以流过此电阻的电流为数百uA为基准,以降低功率损失。 20/24 图18 乘法器的特性曲线族图 第四脚(CS) : 为电流比较器的反向输入端,经由此脚L6561可以知道实时的电感电流,并藉一 外部感测电阻Rs将之转换为一等比例的电压;当此脚的讯号超过由乘法器输出所设定 的临界电压,PWM的栓锁就被重置、MOSFET就被关闭;在PWM栓锁还未被ZCD讯 号设定之前,MOSFET都会在关闭的状态。另有一内部电路作以下动作确认:在第四 脚讯号消失前,PWM栓锁不能被设定。 感测电阻值由下是计算: 其中 Rs上所消耗的功率(如下式)不要超过额定功率的1﹪。 内部1.8V(最大)稽纳二极管将PWM比较器的非反向输入端做限制,已设定临 界电流值,所以流经电阻的最大电流值为 此值也是可以流过电感的最大电流,我们可以使用这个值来确认铁心是否饱和。 第五脚(ZCD) : 此脚为零电流侦测电路的输入脚,经由一限流电阻连接到升压电感的辅助绕组。 零电流侦测电路为负缘触发: 当这脚的电压低于1.6V时PWM栓锁电路设定、 MOSFET 导通;然而,在此之前,电路需先被防护:亦即在此脚电压下降到1.6V之前,此脚需 先有一个由MOSFET关闭所造成的2.1V正缘触发才可以。 最大主/辅助线圈匝数比m,必须确定在MOSFET关闭时,能够传送足够的电压以 防护零电流侦测电路。 假若绕组也有供应IC电源,在Vcc电压范围内上述的原则可能不会兼容。为解决 此一不兼容的问题,图16的自供应网络可以被使用;限流电阻的最小值为,在跨于辅 助绕组最大电压时,有3mA的电流流进此脚。 可以采用微调的方法,使MOSFET导通的时间,恰好发生在泄极震荡电压谷底时 21/24 (完全释能的电感与泄极电容产生震荡,参考图19) ,来得到实际的值,如此可使在 导通时的损耗减为最小。 图19 泄极谐振时的电压图 若是此脚直接由外部驱动讯号驱动,则L6561将于此信号(的负缘)同步。若是 此脚空接,L6561将以内部启动器频率工作;在此情况下,很明显的并非在TM模式操 作、亦不会有高的PF值。但此特性可以在其它应用场合使用。 此脚亦包含了除能(Disable)功能;若是此脚的电压低于150mV时,系统就会关 闭。为了如此,从此脚沉入的电流需10mA以上。IC的静态电流大约将减至1.4mA。 当 外部Pull-down被移除,由于内部150uA产生器将拉高(Pull-up)此脚,系统将会重新 启动。 第六脚(GND) : 此脚做为讯号内部电路电流、与门驱动电流的返回路径。当在Layout PCB板时, 此两条路径应要分开。 第七脚(GD) : 为驱动器的输出,具有提供/沉入400mA的驱动能力。 为了避免当供应芯片的电压 低于UVLO临界准位时所造成的泄漏电流,而造成外部MOSFET多余的导通,内部的 Pull-down电路将使此脚保持为低准位。此电路保证在当 Vcc3V时,此脚的最大电压 为0.3V (Isink=10mA) ; 如此可以允许忘记于闸极与源极间加电阻 (为了达同样目的) 。 22/24 第八脚(Vcc) : 为系统电源的供应脚,此脚与外部的启动电路(经由一个电阻连接到主电源上) 和自供应电路连接。 不论自供应系统的架构为何, 一定有一个电容连接于此脚与地端。 为了启动L6561,此脚的电压必须超过13V(最大值) ;若低于此值则IC并不会工 作,同时从Vcc消耗的电流将小于90uA;并允许使用高启动电阻(数百 KΩ) ,以在低 负载时,降低功率损失和提高系统效率(特别是宽输入范围的应用场合) 。 当系统在操作情况时,损耗的电流(不包含闸极驱动)与操作情况关联,但最大 不超过4.5mA。 IC只有于供应电压在欠电压锁住临界电压(最大10.3V)之上时,才能持续工作; 若是Vcc电压超过内部稽纳二极管18V(额定电流30mA) ,二极管便会动作,做电压箝 住;于此情况下功率损耗会有相当的程度增加。 EE19- 20MAX 19MAX 16MAX 1 BOTTOM VIEW 3 10.5+/-0.5 4 5.0+/0.3 6 4+/-1 23/24 E1,E2 1 4 N2 E2 N1 3 N2 6 N1 E1 BOBBIN EE19(PC40) Lp=700μH(132KHz) 24/24